scaling이 점점 진행됨에 따라 device level의 side-effect가 커지고 있다. circuit designer로서, 그러한 특성을 어떻게 회로적으로 보상해줄지가 중요하다. 기본적인 MOSFET의 동작부터 복습하고 나중에 EKV model, FinFET도 공부해보려고 한다.

2022.02.14. 초안

2.1 MOS Device

transistor 동작의 정성적인 이해를 위해서는 고체물리와 양자역학에 대한 background가 필요하다. 물리전자 과목에서 처음 Energy-band model, p-n junction 등을 배울때 정말 힘들었던 기억이 난다. circuit designer에게는 다소 등한시 될 수도 있는 내용이지만, 우수한 designer로서 꼭 갖추어야할 소양이라고 생각한다. 물리전자, 전자소자 수준의 내용은 반드시 복습하도록 하자.

본글에서는 반도체 물리(Energy-band model, p-n junction 등)에 대한 사전지식이 있다고 보고, 어려운 유도는 생략하겠다.

2.1.1 MOSFET Structure

먼저 MOSFET의 기본구조에 대해서 살펴보자.

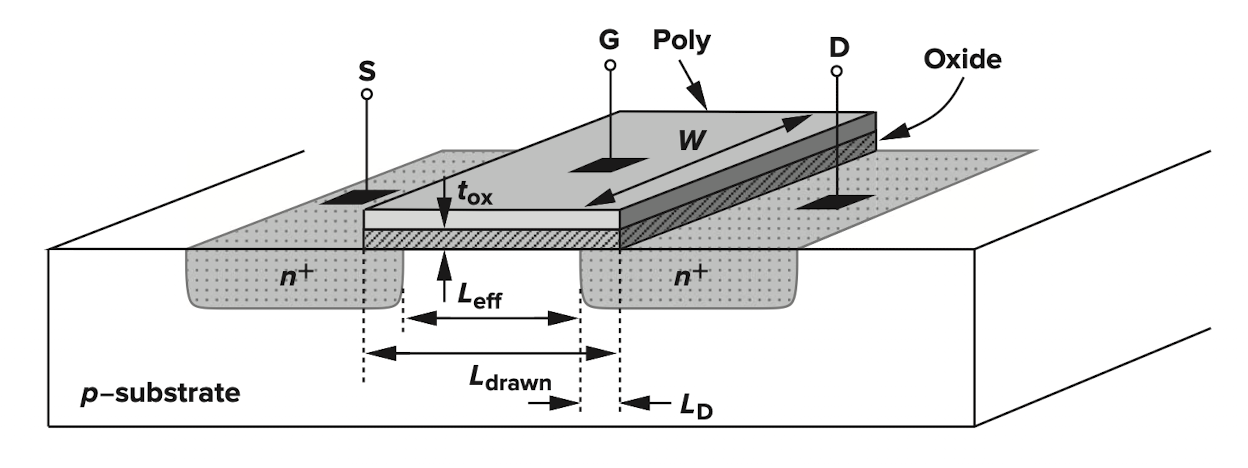

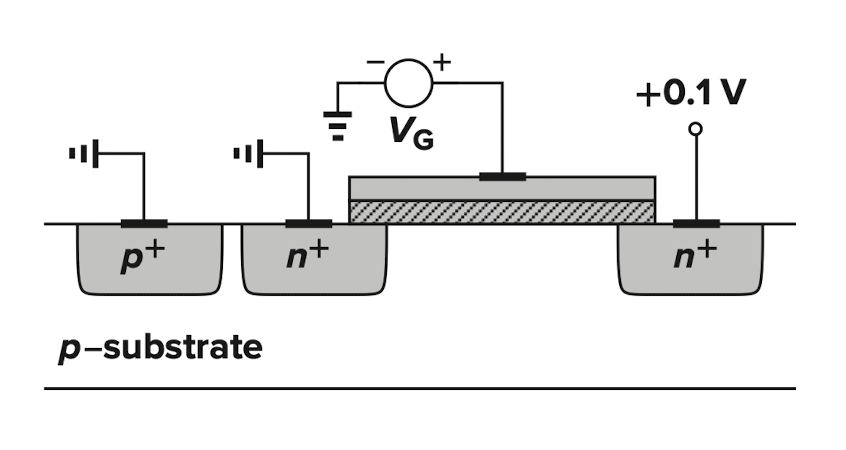

위 그림은 n-type MOSFET의 구조이다. p-type substrate(p-sub, bulk, body)에 heavily-doped n-type(n+)의 Source(S)와 Drain(D)이 존재한다. 그리고 substrate위에는 Oxide(절연체)가 놓이고 그 바로 위에 Poly-silicon(Poly)이 놓인다. MOSFET은 symmetric(좌우대칭)하기 때문에, Source와 Drain의 위치는 바뀔 수 있고 더 높은 전압이 걸리는 곳이 Drain, 낮은 전압이 걸리는 곳이 Source로서 동작한다.

Source와 Drain 사이의 거리를 $L$(Length), 그에 수직하는 방향 길이를 $W$(Width)라고 한다. $L$은 좀더 세분화 되는데, doping 과정에서 Source와 Drain의 doping 영역이 diffusion으로 인해서 변하기 때문이다. 그래서 lateral 방향의 Oxide(혹은 Gate)의 길이(설계한 $L$)를 $L_{drawn}$, 실질적인 Source와 Drain 사이의 길이를 $L_{eff}$로 표기한다. 일반적으로 $L$로 표기되면 $L_{eff}$를 의미한다.

Oxide의 두께는 $t_{ox}$로 나타내고 Capacitance(전기용량) 공식에 의해 $t_{ox}$가 작을수록 큰 $C_{ox}$(Oxide의 capacitance)얻고 소자에서 큰 전류를 얻을 수 있다.

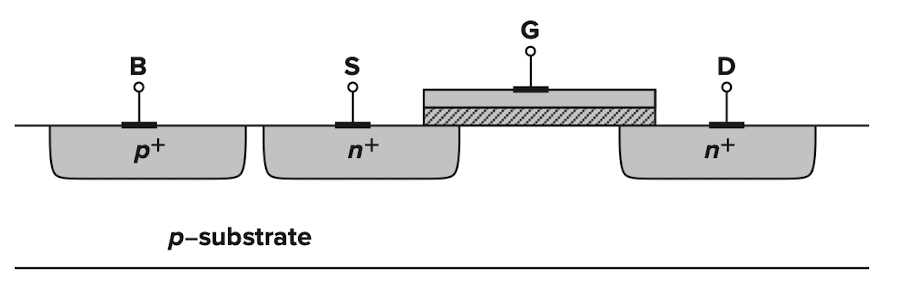

여기에 추가적으로 substrate의 전압을 control하기 위해 추가적으로 Body(B) terminal을 만들어 준다. p-substrate이므로 Ohmic contact을 위해서 heavily-doped p-type 영역에 전압을 걸어줘서 substrate의 전압을 설정한다.

따라서 MOSFET은 Source, Gate, Drain, Body 까지 4-terminal device임을 알 수 있다.

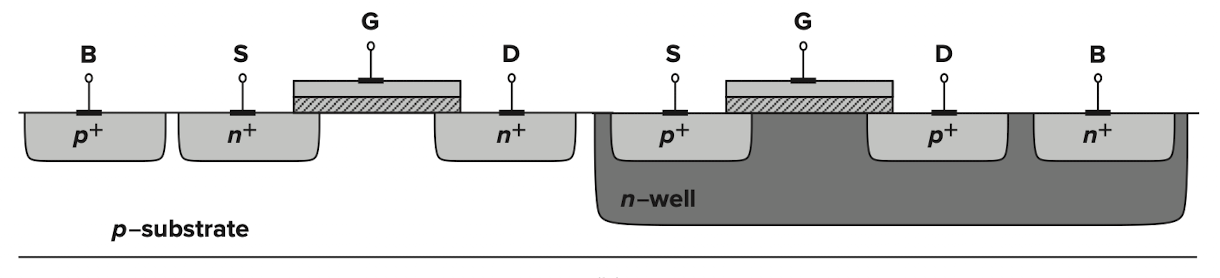

p-type MOSFET(PMOS)은 n-type MOSFET(NMOS)에서 doping type을 반대로 생각하면 된다. CMOS에서, 하나의 substrate 위에 NMOS와 PMOS 모두 만들기 위해 다음과 같이 설계한다.

왼쪽이 NMOS이고 오른쪽이 PMOS이다. PMOS는 n-type substrate를 필요로하기 때문에 p-substrate위에 n-well이라는 영역을 만들어 주고 그 안에서 PMOS를 만든다. 이렇게 만들면 각각의 p-n juction 모두 reverse-bias 상태로 하나의 substrate에 집적이 가능하다.

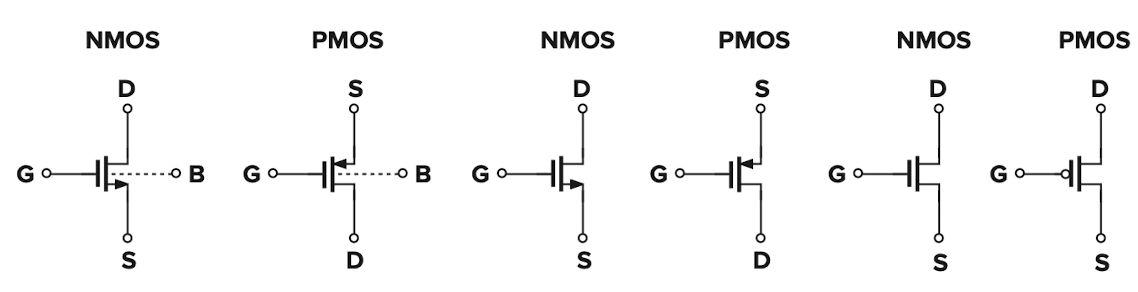

MOSFET의 circuit symbol은 아래와 같다.

- 왼쪽의 두 symbol이 기본적인 4-terminal MOSFET의 symbol이다. circuit에서는 일반적으로 위쪽 방향이 고전압이므로, NMOS에서는 위쪽 terminal이 Drain, PMOS는 Source가 된다.(PMOS에서는 높은 전압에 걸리는 쪽이 Source로서 동작한다)

- 중앙의 두 symbol은 보편적으로 사용하는 symbol이다. circuit 내에서 NMOS의 Body와 PMOS의 Body는 각각 가장 낮은 전압, 가장 높은 전압에 연결되기 때문에(각 소자의 Source/Drain과 Substrate의 reverse-bias를 위해서) 생략해서 사용한다.

- 오른 쪽 두 symbol은 digital 분야에서 사용되는 MOSFET이다. 이때는 MOSFET이 switch로서 동작하기 때문에 Gate에 high voltage가 걸리면 switch가 ON된 것으로 생각하면 된다. PMOS는 Gate에 low voltage가 걸려야 turn-on되기 때문에 symbol에서 Gate에 bubble(active-low)을 그려준다.

2.1.2 Basic Operation of MOSFET

직관적인 수준에서만 동작원리를 살펴보려고한다. NMOS의 각 terminal에 아래와 같이 전압을 인가했다고 생각해보자.

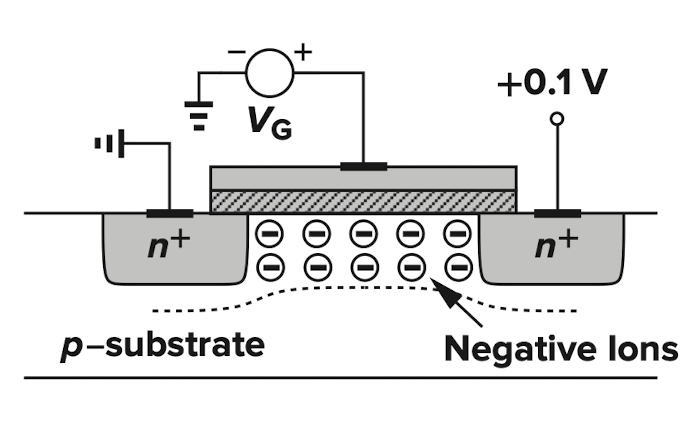

가장 왼쪽이 Body(p-sub에 p+ doping이므로), 그 다음이 Source(오른쪽 n+보다 전압이 낮으므로), 가장 오른쪽이 Drain(Source 대비 전압이 높으므로) terminal이다.

Gate에 0V($V_G = 0$)인 경우에는 p-substrate의 전압도 0V이므로 아무일도 일어나지 않고 전류도 흐를 수 없다.

Gate 전압을 조금씩 키우면, Gate 아래의 영역에 전자들이 모여들면서 acceptor(p-type doping을 만드는 dopant)들과 결합해 Negative Ion을 형성한다. 하지만 이 전자들은 원자에 속박되어 있어서 Sorce와 Drain 사이에 전류가 흐를 수 없다.(점선은 depletion region을 나타낸다)

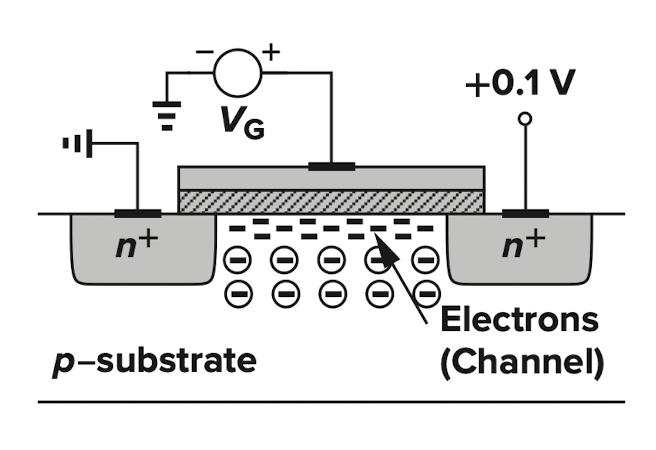

Gate 전압을 더 키우면, Gate 아래의 영역 대부분의 원자들이 이온화 되고 전자들이 free electron(자유전자)으로서 Oxide interface에 쌓이게 된다. 이렇게 만들어진 전자들을 가리켜 channel이라고 하고, 이 channel을 통해서 자유전자들이 Source와 Drain 사이의 current path를 만든다. 결과적으로 Drain에 Source보다 높은 전압을 걸어주면 전류가 흐른다.

이렇게 channel 형성에 필요한 최소한의 Gate 전압을 threshold voltage(문턱전압)이라고 한다.

Appendix

Why Poly-Si Gate?

학부에서는 Gate가 heavily-doped poly-Si라고 주입식으로 배웠을 것이다.

초기에는 Gate에 Aluminum metal이 사용되었지만 후술할 이유로 인해 poly-Si gate로 바뀌었고, 최근에는 high-k dielectrics이 사용됨에 따라 gate에도 High-K Metal Gate(HKMG)가 사용되기 시작하였다.

Poly-Silicon

먼저, Al Gate에서 poly-Si gate로 넘어간 이유에 대해 알아보자.

- Self-aligned Gate Process

초기 공정에서는 Source와 Drain을 만든 이후에 Gate를 만들었다. 이때, gate mask(gate를 만들기 위해 gate 영역만 뚫린 mask)가 misaligned되면 Gate가 Source와 Drain 영역을 침범하면서 parasitic capacitance인 Gate-Source Capacitance($C_{gs}$)와 Gate-Drain Capacitance($C_{gd}$)를 형성하게 된다. $C_{gd}$는 Miller effect로 인해 MOS의 switching speed를 저하시키는 요인으로서 작용한다.

이 문제점을 해결하기 위해 self-aligned gate process가 도입되었다. Source와 Drain을 만들기 이전에, Gate에 Oxide와 poly-Si를 올린다. 이후 doping 과정에서 Source, Gate, Drain 영역을 doping해주면, Oxide가 Mask 역할을 해줌으로써 Source와 Drain 영역이 self-aligned되어 형성된다. 결과적으로 parasitic capacitance($C_{gs}$, $C_{gd}$)를 줄일 뿐만 아니라, Mask의 갯수도 줄일 수 있다.

- Higher melting point

Source와 Drain doping 공정 이후 annealing 공정을 진행하는데 이때 온도가 800℃가 넘는다. 그런데 Aluminum의 녹는점이 약 660℃이기 때문에 그러한 고온에서는 녹아버린다. 반면, poly-Si는 고온에서도 버틸 수 있다.

undoped poly-Si는 저항이 상대적으로 크기 때문에, metal(low resistive) 대신에 사용하기 위해서 doping 과정을 통해 저항을 낮춘다.

- Threshold voltage

MOSFET의 threshold voltage는 Gate의 work function에 영향을 받는다. Metal gate의 work function을 바꾸기 위해서는 metal 자체를 변경해야하지만, poly-Si는 doping density를 조절함으로써 work function을 조절할 수 있다. 결과적으로 threshold voltage를 조절할 수 있다.

HKMG

위와 같은 이유로 Aluminum에서 poly-Si로 넘어갔다.

그런데 공정상의 한계로 더이상의 소형화가 어려워지자, Gate capacitance를 키우기 위해 $t_{ox}$를 줄이는 대신 절연체의 물질을 바꾸는 방향으로 연구하게 된다. 그래서 Oxide영역에 $SiO_2$대신 high-k dielectrics을 사용하기 시작한다.

poly-Si와 high-k dielectrics 조합으로 소자를 만들면 아래와 같은 문제점이 발생한다.

- Silicide

high-k dielectrics(Hf- 과 Zr-base의 dielectrics이 많이 사용된다)은 고온에서 poly-Si와 반응하여 silicide(Silicon과 금속의 화합물)를 형성하게 된다.

- High threshold voltage

그리고 high-k dielectircs은 기존의 $SiO_2$대비 electron affinity가 크고 bandgap이 좁아, poly-Si와 high-k dielectrics 조합의 MOS는 threshold voltage가 커진다. threshold voltage가 커지면 supply volatge를 낮추기 어렵고 소자의 속도도 느려진다.

그래서 다시 Gate에 poly-Si 대신 Metal Gate를 사용하게 되었다.

Why lightly-doped p-type substrate?

CMOS 공정을 보면 substrate는 항상 lightly-doped p-type으로 doping되어있다. NMOS를 만들기 위해서 p-sub가 필요한 것은 맞지만 이 때문에 PMOS를 만들기 위해서 n-well을 추가적으로 만들어줘야한다. 그런데 n-substrate를 사용해서 p-well을 만들고 그 위에 NMOS를 만들어 줘도 CMOS 구현이 가능하다. 왜 p-substrate를 사용하고, 하필 lightly-doped일까?

- electron mobility

electron(전자) mobility는 hole(양공) mobility 보다 크기 때문에, 동일 조건에서 NMOS는 PMOS 대비 더 빠르게 동작한다. 특히, electron mobility는 p-substrate가 heavily-dope일 때보다 lightly-doped일 때가 더 크다.

만약 n-substrate 위에 p-well을 만들어서 NMOS를 구현한다면, p-well의 doping density는 n-substrate보다 커야하므로 electron mobility가 감소한다.

그래서 가장 좋은 성능의 NMOS를 얻기 위해, "lightly-doped" "p"-type substrate를 기본으로 사용한다.

'전자공학 > Circuits' 카테고리의 다른 글

| [MOSFET 03] Second-order Effect (0) | 2022.02.17 |

|---|---|

| [MOSFET 02] MOSFET I/V Characteristics (0) | 2022.02.17 |

| Introduction of Analog Design (0) | 2022.02.14 |